Main Page

From The Emerging Circuits and Computation Group at ITU

(Difference between revisions)

| (27 intermediate revisions by one user not shown) | |||

| Line 9: | Line 9: | ||

| valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | ||

| − | Our group, comprised of [[Mustafa_Altun|'''Mustafa Altun''']] and his [[People|scholars & students]], is in the [http:// | + | Our group, comprised of [[Mustafa_Altun|'''Mustafa Altun''']] and his [[People|scholars & students]], is in the [http://ehb.itu.edu.tr/en/home Department of Electronics and Communication Engineering] at [http://www.itu.edu.tr/en/ Istanbul Technical University]. In terms of [[Research|'''research''']], we aim to develop new computing paradigms as well as circuit design and electronic design automation (EDA) techniques especially for future and emerging technologies. We also have a special interest in electronics reliability in both circuit and system levels. In terms of [[Teaching|'''teaching''']], we offer courses on digital/analog circuit design as well as on computational nanoelectronics. |

[[Image:website-art-1.png|center|none|550px|link=]] | [[Image:website-art-1.png|center|none|550px|link=]] | ||

| Line 24: | Line 24: | ||

| style="padding:2px;" | <h2 id="mp-tafi-h2" style="margin:3px; background:#8FBC8F; font-size:125%; font-weight:bold; border:1px solid #3CB371; text-align:left; color:#000; padding:0.2em 0.4em;">Group news</h2> | | style="padding:2px;" | <h2 id="mp-tafi-h2" style="margin:3px; background:#8FBC8F; font-size:125%; font-weight:bold; border:1px solid #3CB371; text-align:left; color:#000; padding:0.2em 0.4em;">Group news</h2> | ||

| + | |||

| + | * <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> Nov. 2020</span> We have received TUBITAK Project Performance Award given to our completed TUBITAK 3501 project on ''computing with nano-crossbar arryas" for its outcomes and future impacts. | ||

| + | |||

| + | * <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> Oct. 2020</span> We have received TUBITAK Project Performance Award given to our completed TUBITAK 1002 project on ''reversible computing for fault tolerance" for its outcomes and future impacts. | ||

| + | |||

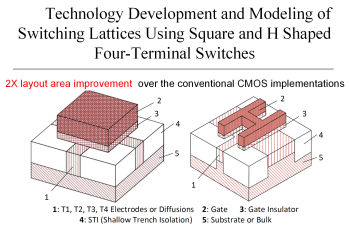

| + | * <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> Sept. 2020</span> Our patent "''CMOS compatible device based on four-terminal switching lattices''" is granted by the U.S. Patent and Trademark Office. | ||

| + | |||

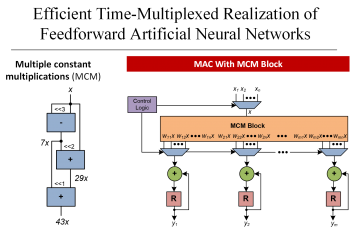

| + | * <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> May 2020</span> We will present our work "''Efficient Hardware Implementation of Artificial Neural Networkcompleted s Using Approximate Multiply-Accumulate Blocks''" in [http://www.isvlsi.org/ IEEE-ISVLSI 2020]. | ||

* <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> Apr. 2020</span> Our project on ''hardware implementation of artificial neural networks'' received a grant from the TUBITAK Scientific and Technological Research Projects Funding Program (1001). | * <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> Apr. 2020</span> Our project on ''hardware implementation of artificial neural networks'' received a grant from the TUBITAK Scientific and Technological Research Projects Funding Program (1001). | ||

| Line 41: | Line 49: | ||

* <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> Oct. 2019</span> We will give a keynote talk "''Computing with Nano-crossbar Arrays''" in [http://www.iaria.org/conferences2019/CENICS19.html CENICS 2019]. | * <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> Oct. 2019</span> We will give a keynote talk "''Computing with Nano-crossbar Arrays''" in [http://www.iaria.org/conferences2019/CENICS19.html CENICS 2019]. | ||

<!--* <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> July 2019</span> We hire! For current openings, click [[Media:ECC-ANN-position-2019.pdf | '''here''']] and [[Media:ECC-nano-position-2019.pdf | '''here''']].--> | <!--* <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> July 2019</span> We hire! For current openings, click [[Media:ECC-ANN-position-2019.pdf | '''here''']] and [[Media:ECC-nano-position-2019.pdf | '''here''']].--> | ||

| + | |||

| + | <div class="toccolours mw-collapsible mw-collapsed" cellspacing="0" cellpadding="0" width=100% style="border:1px solid #3CB371; padding:1px;"> | ||

| + | :<u>'''PREVIOUS NEWS'''</u>: | ||

| + | <div class="mw-collapsible-content"> | ||

* <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> July 2019</span> We will present our work "''The Enhanced Electronic Properties of P3HT-WO3 Hybrid Thin Film Transistors''" in [http://www.advanced-nanomaterials-conference.com/ ANM 2019]. | * <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> July 2019</span> We will present our work "''The Enhanced Electronic Properties of P3HT-WO3 Hybrid Thin Film Transistors''" in [http://www.advanced-nanomaterials-conference.com/ ANM 2019]. | ||

| Line 47: | Line 59: | ||

* <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> Apr. 2019</span> We will present our work "''Implementation of CMOS Logic Circuits with Perfect Fault Detection Using Preservative Reversible Gates''" in a leading conference on online testing [http://tima.univ-grenoble-alpes.fr/conferences/iolts/iolts19/ IOLTS 2019]. | * <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> Apr. 2019</span> We will present our work "''Implementation of CMOS Logic Circuits with Perfect Fault Detection Using Preservative Reversible Gates''" in a leading conference on online testing [http://tima.univ-grenoble-alpes.fr/conferences/iolts/iolts19/ IOLTS 2019]. | ||

| − | |||

| − | |||

| − | |||

| − | |||

* <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> Nov. 2018</span> We will present our work "''Realization of Four-Terminal Switching Lattices: Technology Development and Circuit Modeling''" in a premier conference on electronic design automation [http://www.date-conference.com/ DATE 2019]. | * <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> Nov. 2018</span> We will present our work "''Realization of Four-Terminal Switching Lattices: Technology Development and Circuit Modeling''" in a premier conference on electronic design automation [http://www.date-conference.com/ DATE 2019]. | ||

| Line 136: | Line 144: | ||

</div> | </div> | ||

| − | <h2 id="mp-tafi-h2" style="margin:3px; background:#8FBC8F; font-size:125%; font-weight:bold; border:1px solid #3CB371; text-align:left; color:#000; padding:0.2em 0.4em;">Our progress by the numbers, 2013- | + | <h2 id="mp-tafi-h2" style="margin:3px; background:#8FBC8F; font-size:125%; font-weight:bold; border:1px solid #3CB371; text-align:left; color:#000; padding:0.2em 0.4em;">Our progress by the numbers, 2013-2020</h2> |

| − | Founded in 2013, our group has made many achievements | + | Founded in 2013, our group has made many achievements including: |

| − | * <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> 1. | + | * Nearly <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> $1.075.000</span> was received to be spent for our group. <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> $400.000</span> came from an international '''EU H2020''' project; <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> $100.000</span> came from an international '''TUBITAK-NSF''' project; and <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> $500.000</span> came from six different national '''TUBITAK''' projects. We are the principal investigator ('''PI''') of all these <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> 8</span> projects. Additionally, <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> $50.000</span> came directly from our '''industry''' partners and <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> $25.000</span> came from '''university-internal''' sources. |

| + | * <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> 61</span> peer-reviewed '''papers''' were published/accepted in leading journals and conferences. <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> 36</span> of them are solely '''made in ECC''' -- all authors are from our group; <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> 10</span> of them are coauthored by our collaborators from '''industry'''; and <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> 21</span> of them are coauthored by our collaborators from '''academia'''. | ||

| − | * <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> | + | * <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> 3</span> '''patents''' were granted. Two of them are '''US''' patents and one of them is a '''TR''' patent. |

| − | * <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> | + | * <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> 10</span> '''Masters''' students graduated from our group; <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> 6</span> '''Doctoral''' students are expected to graduate by 2023; and <span style="background:#F5F5F5; font-size: 125%; border:2px solid #B22222;"> 2</span> '''Posdoctoral''' researchers joined us. |

| − | [[Image: | + | [[Image:2023-vision.png|center|none|550px|link=]] |

|} | |} | ||

| style="border:1px solid transparent;" | | | style="border:1px solid transparent;" | | ||

| Line 160: | Line 169: | ||

* For current '''open positions''' [[Media:Altun-Tubitak-3501-is-ilani-2014.pdf | '''click here''']]. --> | * For current '''open positions''' [[Media:Altun-Tubitak-3501-is-ilani-2014.pdf | '''click here''']]. --> | ||

* Visiting '''professors/researchers''' and '''postdoc''' scholars are very welcome. They are highly encouraged to apply for the following programs: | * Visiting '''professors/researchers''' and '''postdoc''' scholars are very welcome. They are highly encouraged to apply for the following programs: | ||

| − | ** European Union H2020 Individual Fellowships ([ | + | ** European Union H2020 Individual Fellowships ([https://ec.europa.eu/research/mariecurieactions/actions/individual-fellowships_en MSCA - IF]) |

** TUBITAK Research Fellowship Program For Foreign Citizens ([http://www.tubitak.gov.tr/en/funds/academy/international-researchers-fellowship-programmes/content-2216-research-fellowship-programme-for-international-researchers 2216]) | ** TUBITAK Research Fellowship Program For Foreign Citizens ([http://www.tubitak.gov.tr/en/funds/academy/international-researchers-fellowship-programmes/content-2216-research-fellowship-programme-for-international-researchers 2216]) | ||

** TUBITAK National Postdoctoral Research Fellowship Program ([http://www.tubitak.gov.tr/tr/burslar/doktora-sonrasi/arastirma-burs-programlari/icerik-2218-yurt-ici-doktora-sonrasi-arastirma-burs-programi 2218]) | ** TUBITAK National Postdoctoral Research Fellowship Program ([http://www.tubitak.gov.tr/tr/burslar/doktora-sonrasi/arastirma-burs-programlari/icerik-2218-yurt-ici-doktora-sonrasi-arastirma-burs-programi 2218]) | ||

| Line 178: | Line 187: | ||

* We are dedicated to establish new partnerships for [http://ec.europa.eu/programmes/horizon2020/ '''EU H2020'''] work programmes including, but not limited to: | * We are dedicated to establish new partnerships for [http://ec.europa.eu/programmes/horizon2020/ '''EU H2020'''] work programmes including, but not limited to: | ||

** Future and Emerging Technologies ([http://ec.europa.eu/programmes/horizon2020/en/h2020-section/future-and-emerging-technologies FET]) | ** Future and Emerging Technologies ([http://ec.europa.eu/programmes/horizon2020/en/h2020-section/future-and-emerging-technologies FET]) | ||

| − | ** Information and Communication Technologies ([http://ec.europa.eu/digital-agenda/en/information-communication-technologies-horizon-2020 ICT]) | + | ** Information and Communication Technologies ([http://ec.europa.eu/digital-agenda/en/information-communication-technologies-horizon-2020 ICT]) |

<!--** Cluster for Application and Technology Research in Europe on NanoElectronics ([http://www.catrene.org/index.php CATRENE]) | <!--** Cluster for Application and Technology Research in Europe on NanoElectronics ([http://www.catrene.org/index.php CATRENE]) | ||

** The projects needed expertise in reliability, circuit design, and electronic design automation --> | ** The projects needed expertise in reliability, circuit design, and electronic design automation --> | ||

| − | * We are dedicated to establish new partnerships within [http:// | + | * We are dedicated to establish new partnerships within [http://www.cost.eu/ '''EU Cost'''] actions and [http://www.tubitak.gov.tr/tr/uluslararasi/ikili-proje-destekleri/icerik-basvuruya-acik-programlar '''joint international'''] calls. |

* We are also interested in industry based and market driven partnerships through [http://www.eurekanetwork.org/ '''EUREKA''']. | * We are also interested in industry based and market driven partnerships through [http://www.eurekanetwork.org/ '''EUREKA''']. | ||

[[Image:Funding-7.png|center|none|450px|link=http://www.ecc.itu.edu.tr/index.php?title=Projects]] | [[Image:Funding-7.png|center|none|450px|link=http://www.ecc.itu.edu.tr/index.php?title=Projects]] | ||

| Line 198: | Line 207: | ||

<div><center> | <div><center> | ||

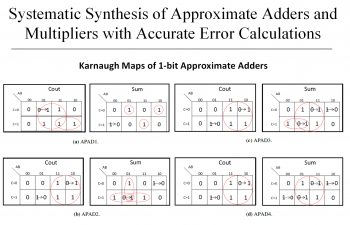

| − | <li style="display: inline-block;"> [[File:Main-pub-1-2019.png|link=http://www.ecc.itu.edu.tr/images/c/c8/Nojehdeh_Altun_Approximate_Adders_Multipliers.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/c/c8/Nojehdeh_Altun_Approximate_Adders_Multipliers.pdf The paper] published in [http://www.journals.elsevier.com/integration Integration], | + | <li style="display: inline-block;"> [[File:Main-pub-3-2020.png|link=http://www.ecc.itu.edu.tr/images/6/69/Akkan_EtAl_H_and_Square_Lattice_Technology_Development.pdf |thumb|none|350px|[http://www.ecc.itu.edu.tr/images/6/69/Akkan_EtAl_H_and_Square_Lattice_Technology_Development.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6245516 IEEE TETC], 2020]] |

| + | <li style="display: inline-block;"> [[File:Main-pub-1-2020.png|link=http://www.ecc.itu.edu.tr/images/e/eb/Aksoy_Parvin_Nojehdeh_Altun_Time_Multiplexed_ANN_Implementation.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/e/eb/Aksoy_Parvin_Nojehdeh_Altun_Time_Multiplexed_ANN_Implementation.pdf The paper] presented at [http://iscas2020.org/ IEEE ISCAS], 2020]] | ||

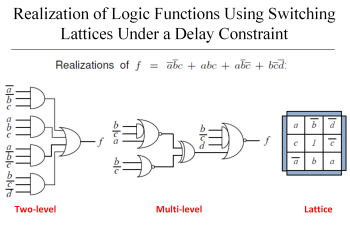

| + | <li style="display: inline-block;"> [[File:Main-pub-2-2020.png|link=http://www.ecc.itu.edu.tr/images/5/55/Aksoy_EtAl_Logic_Synthesis_for_Switching_Lattices_under_Delay_Constraint.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/5/55/Aksoy_EtAl_Logic_Synthesis_for_Switching_Lattices_under_Delay_Constraint.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=43 IEEE TCAD], 2020]] | ||

| + | <li style="display: inline-block;"> [[File:Main-pub-1-2019.png|link=http://www.ecc.itu.edu.tr/images/c/c8/Nojehdeh_Altun_Approximate_Adders_Multipliers.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/c/c8/Nojehdeh_Altun_Approximate_Adders_Multipliers.pdf The paper] published in [http://www.journals.elsevier.com/integration Integration], 2020]] | ||

| + | <!-- | ||

<li style="display: inline-block;"> [[File:Main-pub-2-2019.png|link=http://www.ecc.itu.edu.tr/images/5/5c/Akkan_Altun_Sedef_OFET_Modelling_IEEE_Access.pdf|thumb|none|347px|[http://www.ecc.itu.edu.tr/images/5/5c/Akkan_Altun_Sedef_OFET_Modelling_IEEE_Access.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6287639 IEEE Access], 2019]] | <li style="display: inline-block;"> [[File:Main-pub-2-2019.png|link=http://www.ecc.itu.edu.tr/images/5/5c/Akkan_Altun_Sedef_OFET_Modelling_IEEE_Access.pdf|thumb|none|347px|[http://www.ecc.itu.edu.tr/images/5/5c/Akkan_Altun_Sedef_OFET_Modelling_IEEE_Access.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6287639 IEEE Access], 2019]] | ||

<li style="display: inline-block;"> [[File:Main-pub-3-2019.png|link=http://www.ecc.itu.edu.tr/images/e/e0/Aksoy_Altun_Realizations_with_Switching_Lattices.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/e/e0/Aksoy_Altun_Realizations_with_Switching_Lattices.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=12 IEEE TC], 2019]] | <li style="display: inline-block;"> [[File:Main-pub-3-2019.png|link=http://www.ecc.itu.edu.tr/images/e/e0/Aksoy_Altun_Realizations_with_Switching_Lattices.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/e/e0/Aksoy_Altun_Realizations_with_Switching_Lattices.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=12 IEEE TC], 2019]] | ||

<li style="display: inline-block;"> [[File:Main-pub-4-2019.png|link=http://www.ecc.itu.edu.tr/images/c/c9/Tunali_Altun_Multiple_type_Defect_Tolerance_in_Nano_Crossbar_Arrays.pdf|thumb|none|352px|[http://www.ecc.itu.edu.tr/images/c/c9/Tunali_Altun_Multiple_type_Defect_Tolerance_in_Nano_Crossbar_Arrays.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6245516 IEEE TETC], 2019]] | <li style="display: inline-block;"> [[File:Main-pub-4-2019.png|link=http://www.ecc.itu.edu.tr/images/c/c9/Tunali_Altun_Multiple_type_Defect_Tolerance_in_Nano_Crossbar_Arrays.pdf|thumb|none|352px|[http://www.ecc.itu.edu.tr/images/c/c9/Tunali_Altun_Multiple_type_Defect_Tolerance_in_Nano_Crossbar_Arrays.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6245516 IEEE TETC], 2019]] | ||

| − | |||

| − | |||

<li style="display: inline-block;"> [[File:Main-pub-5-2018.png|link=http://www.ecc.itu.edu.tr/images/7/7d/Altun_Parvin_Cilasun_Exploiting_Reversible_Computing_for_CMOS_Fault_Tolerance.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/7/7d/Altun_Parvin_Cilasun_Exploiting_Reversible_Computing_for_CMOS_Fault_Tolerance.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6287639 IEEE Access], 2018]] | <li style="display: inline-block;"> [[File:Main-pub-5-2018.png|link=http://www.ecc.itu.edu.tr/images/7/7d/Altun_Parvin_Cilasun_Exploiting_Reversible_Computing_for_CMOS_Fault_Tolerance.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/7/7d/Altun_Parvin_Cilasun_Exploiting_Reversible_Computing_for_CMOS_Fault_Tolerance.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6287639 IEEE Access], 2018]] | ||

<li style="display: inline-block;"> [[File:Main-pub-4-2018.png|link=http://www.ecc.itu.edu.tr/images/d/db/Tunali_Morgul_Altun_Defect_Tolerant_Memristor_Crossbars.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/d/db/Tunali_Morgul_Altun_Defect_Tolerant_Memristor_Crossbars.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=40 IEEE Micro], 2018]] | <li style="display: inline-block;"> [[File:Main-pub-4-2018.png|link=http://www.ecc.itu.edu.tr/images/d/db/Tunali_Morgul_Altun_Defect_Tolerant_Memristor_Crossbars.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/d/db/Tunali_Morgul_Altun_Defect_Tolerant_Memristor_Crossbars.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=40 IEEE Micro], 2018]] | ||

Revision as of 16:22, 14 November 2020

Welcome to the Emerging Circuits and Computation (ECC) Group | |

|

Our group, comprised of Mustafa Altun and his scholars & students, is in the Department of Electronics and Communication Engineering at Istanbul Technical University. In terms of research, we aim to develop new computing paradigms as well as circuit design and electronic design automation (EDA) techniques especially for future and emerging technologies. We also have a special interest in electronics reliability in both circuit and system levels. In terms of teaching, we offer courses on digital/analog circuit design as well as on computational nanoelectronics.  | |

|

|

|

Selected recent publications |

Group pictures |