## Design of Positive Feedback Driven Current-Mode Amplifiers Z-Copy CDBA and CDTA, and Filter Applications

Ersin Alaybeyoğlu<sup>1</sup>, Arda Güney<sup>2</sup>, Mustafa Altun<sup>1</sup> and Hakan Kuntman<sup>1</sup>

Abstract— In this study, high-performance current-mode amplifiers Z-Copy CDBA and CDTA are designed. In order to improve input impedances of the amplifiers, a new approach based on positive feedback is proposed. Impedance improvement/reduction is achieved by using only two extra transistors for each input. This number of extra transistors is very few compared to that in conventional negative feedback based improvement techniques. The proposed technique is justified by performing a detailed stability analysis. It is shown that the input impedances of ZC-CDBA and ZC-CDTA can be safely reduced to the level of  $50\Omega$  by considering fabrication scatterings. The proposed amplifiers are verified with analog filter applications, a new KHN and recently proposed biquadratic and frequency agile filters. It is shown that the filters operate accurately at the frequency level of 100MHz. This is a clear sign of the proposed amplifiers' high performance. Layout and post layout simulations are done for the proposed circuits using AMS 0.18 µm parameters in Cadence environment.

Index Terms—Positive feedback, CMOS integrated circuits, Active filters, Current-mode circuits

## I. INTRODUCTION

Current-mode analog circuits have been well investigated over the last decades as alterative of their voltage-mode counterparts. With the increasing importance of using low voltage supplies, current-mode circuits have recently attracted even more attention. Unlike conventional voltage-mode amplifiers whose DC swing performance is limited by voltage supplies, current-mode amplifiers can satisfactorily operate in low voltage values. Furthermore, current-mode amplifiers have significant advantages such as inherent wide bandwidth, wide dynamic range and simple circuitry with lover voltage supplies [1-2]. In this study, we propose new current-mode circuit structures for "Z Copy Current Differencing Buffered Amplifier (ZC-CDBA)" and "Z Copy Current Differencing Trans-conductance Amplifier (ZC-CDTA)" recommended as versatile current mode analog building blocks by D. Biolek [3]. With an addition of the Z-Copy

<sup>1</sup>Istanbul Technical University, Department of Electronics and Communication Engineering, Istanbul, Turkey (ealaybeyoglu@itu.edu.tr, altunmus@itu.edu.tr, kuntman@itu.edu.tr)

<sup>2</sup>Yildiz Technical University, Department of Electronics and Communication Engineering, Istanbul, Turkey (aguney@yildiz.edu.tr)

terminal, the universality of CDBA [4-5] and CDTA [6-7] was improved. A conventional current mirror or the third generation current conveyor can be used to achieve Z-Copy output current [8].

For the proposed amplifiers, we first focus on achieving low input impedance values that is very beneficial and necessary for current amplifiers. Current amplifiers ideally have zero input impedances. Indeed, input impedance values determine the minimum required resistance values in application circuits. For example, if a current amplifier, in filter application, has an input impedance of  $5k\Omega$  then the resistor values of the filter should be chosen at least  $50k\Omega$  for proper operation. This also affects the minimum required capacitor values of the filter. Considering that resistors and capacitors occupy most of the circuit (layout) area, low input impedance/resistance is essential for current amplifiers. In the literature, reducing the input resistance values is mostly achieved by using negative feedback with an additional amplifier [9-11]. This technique works properly at the cost of an extra amplifier that significantly increase the circuit area and worsens the amplifier's frequency response. In this study, we propose a new way of reducing input resistance values: using positive feedback. The reduction is achieved by using only two extra transistors for each input. Since the input stage of the amplifiers is a current differencing unit with two inputs P and N, total of four extra transistors are needed.

We design the output stage of the proposed ZC-CDBA as a voltage buffer. The amplifier has high impedance Z and Z-Copy terminals, and a low impedance W terminal. We design the output stage of the proposed ZC-CDTA as a floating current source. The amplifier has high impedance X-, X+, Z, and Z-Copy output terminals.

This paper is organized as follows. In the second section, the proposed reduction method for input impedance is introduced. Comparison of the method with conventional methods is presented. In third section, the CMOS implementations and layouts of ZC-CDBA and ZC-CDTA are given. The impedance characteristics of the current mode active blocks are shown at the beginning of this section. Additionally, the impedance values are justified by performing a detailed stability analysis. The stability and worst case analysis for the amplifier's input impedances are shown at the second part of this section. The other characteristics of ZC-CDBA and ZC-CDTA are also given in the same section. In the last section, two current mode filter applications are presented. The first proposed filter contains two ZC-CDBAs, two grounded capacitors, and one resistor. The second filter, frequency agile filter, contains ZC-CDTA and ECCII

(electronically controllable second generation current conveyor). The performance of the filters is tested in this section. Sensitivity values of the filters are also given.

## II. REDUCTION METHOD FOR INPUT IMPEDANCE

In this section positive feedback technique for reducing input impedance is studied. The advantages of using positive feedback are formulized with circuit diagrams.

#### A. Positive Feedback versus Negative Feedback

Reducing input resistance values is conventionally achieved by using negative feedback based methods. In this study, we propose a method based on positive feedback for this purpose. The proposed method with a comparison of the conventional one is analyzed in details.

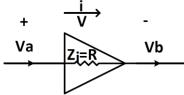

Fig. 1 shows a system without feedback. The internal impedance value of a general system is the ratio of the voltage over the system to the current which flows inside of the system according to Ohm's law. The internal impedance for Fig. 1 is given in Equation 1. The internal impedance is equal to R for purely resistive circuits.

$$Z_{i} = \frac{V}{i} = \frac{V_{b} - V_{a}}{i} = R \tag{1}$$

Fig. 1 A system without feedback

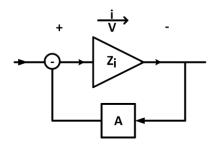

Fig. 2 shows the negative feedback system to reduce the input impedance. Equation 2 gives the internal impedance value for negative feedback system. In this equation,  $AZ_i$  represents the reduction factor; the larger the reduction factor the smaller the resistance values obtained. For example, if an amplifier has an input impedance of 10 k $\Omega$  and 100  $\Omega$  is required for a certain application then this reduction factor is approximately 100 ( $10k\Omega/100\Omega$ ).

Fig. 2 The negative feedback system; input is voltage

$$\frac{V}{i} = \left(\frac{1}{1 + AZ_i}\right)Z_i \tag{2}$$

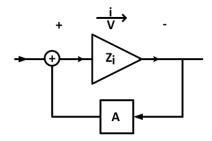

Fig. 3 shows the positive feedback system to reduce the input impedance. Equation 3 gives the internal impedance value for positive feedback system. In this equation,  $AZ_i$

represents the reduction factor; the closer the reduction factor to 1 the smaller the resistance values obtained. For example, if an amplifier has an input impedance of 10 k $\Omega$  and 100  $\Omega$  is required for a certain application then this reduction factor is approximately 1  $(1-100\Omega/10k\Omega)$ .

Fig. 3 The positive feedback system; input is current

$$\frac{V}{i} = (1 - AZ_i)Z_i \tag{3}$$

In order to achieve a certain reduction factor for negative feedback based method, an amplifier with a gain that equals to the reduction factor, should be added [11-12]. For example, if a reduction factor of 100 is needed then an amplifier with a gain of 100 should be added to the original circuit. This is quite costly in terms of the number of added transistors. On the other hand, in order to achieve a certain reduction factor for positive feedback based method, an amplifier with a gain of approximately unity should be added. In this study this is achieved with using only two added transistors. The current differencing unit CMOS realization without any feedback system is given in Fig. 4. The added (extra) circuitries for negative feedback are given in Fig. 5. The proposed reduction method is shown in Fig. 6.

The basic differential pair used as an amplifier to provide negative feedback system is not enough to obtain lower impedance values compared with positive feedback technique. Two stages operational amplifier must be designed to achieve 50 Ohms impedance levels. In this case, the CMOS realization of the current differencing unit has not only very large chip area but also has very complicated CMOS realization. Note that the negative feedback structure uses two extra amplifiers (8 transistors) compared to 4 extra transistors used in the positive feedback structure. The input impedance comparison for the current differencing CMOS realization without feedback, with positive feedback and negative feedback is given in Table I. The values in the table are clearly in favor of using positive feedback. With positive feedback, nearly 10 times smaller resistance values are achieved compared to those with negative feedback.

TABLE I THE INPUT IMPEDANCE COMPARISON

|                               | Without<br>Feedback | Negative<br>Feedback | Positive<br>Feedback |

|-------------------------------|---------------------|----------------------|----------------------|

| N Terminal<br>Input Impedance | 1.2kΩ               | 724Ω                 | 57Ω                  |

| P Terminal<br>İnput Impedance | $1.3k\Omega$        | 653Ω                 | $44\Omega$           |

The only disadvantage of using positive feedback can be the stability problem. For defeating this problem, a detailed

stability analysis is performed in the next section, and it is shown that the input impedance values as low as 50  $\Omega$  can safely be implemented.

Fig. 4 The current differencing CMOS realization without feedback

**Fig. 5** The current differencing CMOS realization with negative feedback

**Fig. 6** The current differencing CMOS realization with positive feedback

# III. CURRENT-MODE AMPLIFIERS (ZC-CDBA AND ZC-CDTA)

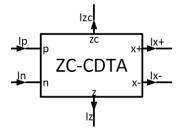

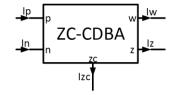

The block diagrams for ZC-CDTA and ZC-CDBA are given in Fig. 7 and Fig. 8, respectively.

Fig. 7 ZC-CDTA block diagram

Fig. 8 ZC-CDBA block diagram

ZC-CDTA has two input terminals and four output terminals. The input terminals are low impedance nodes. The output terminals are high impedance nodes. ZC-CDBA has two input terminals and three output terminals. The input terminals are low impedance nodes. Two of the output terminals (Z, Z copy) are high impedance and the other (W) is low impedance nodes.

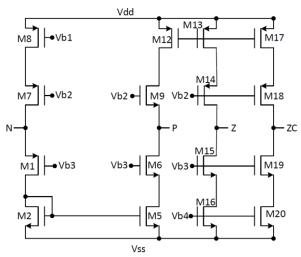

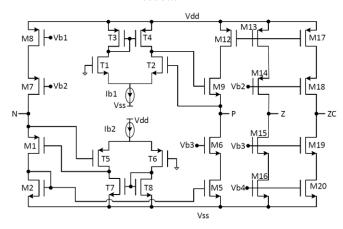

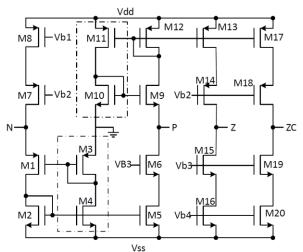

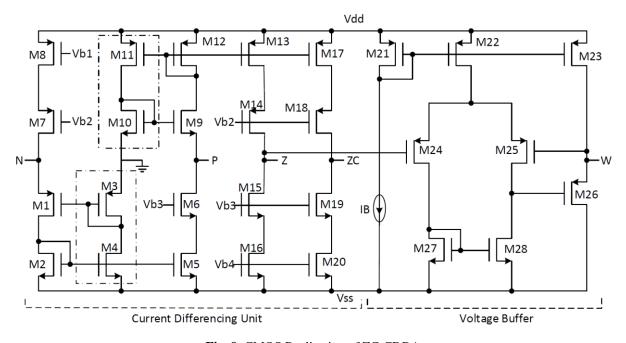

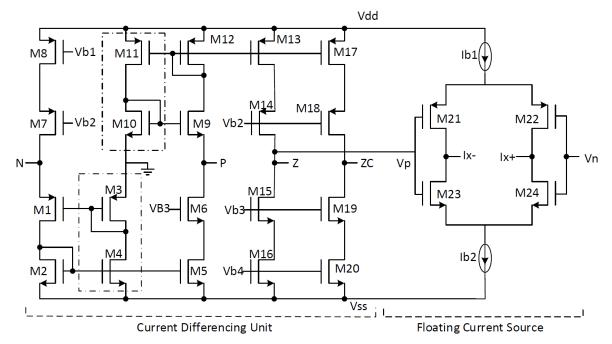

The proposed CMOS structure of the ZC-CDBA and ZC-CDTA are shown in Fig. 9 and Fig. 10, respectively. The equation matrix of the ZC-CDBA is given in Equation 4. In Equation 5 shows the equation matrix of ZC-CDTA.

$$\begin{pmatrix} V_p \\ V_n \\ i_z \\ i_x \\ i_{zc} \end{pmatrix} = \begin{pmatrix} 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 \\ 1 & -1 & 0 & 0 & 0 \\ 0 & 0 & 0 & \pm g_m & 0 \\ 0 & 0 & 0 & 0 & 1 \end{pmatrix} \begin{pmatrix} i_p \\ i_n \\ V_x \\ V_z \\ i_z \end{pmatrix} \tag{5}$$

M1-M20 transistors of the ZC-CDBA and the ZC-CDTA belong to the current differencing unit, which has Z and Z copied output. M21-M28 transistors of the ZC-CDBA are the voltage buffer's transistors. M1-M4 transistors of the ZC-CDTA are the floating current source's transistors [13]. Transistor ratios of ZC-CDBA are shown in Table II. Transistor ratios of ZC-CDTA are shown in Table III.

**TABLE II** TRANSISTOR RATIOS OF ZC-CDBA.

| Transistors | W(µm) | L(µm) |

|-------------|-------|-------|

| M1          | 12    | 0.36  |

| M2          | 120   | 0.36  |

| M3 - M5     | 12    | 0.36  |

| M6 - M9     | 12    | 0.36  |

| M10         | 120   | 0.36  |

| M11 - M25   | 12    | 0.36  |

| M26         | 60    | 0.36  |

| M27 - M28   | 12    | 0.36  |

TABLE III TRANSISTOR RATIOS OF ZC-CDTA.

| Transistors | W(µm) | L(µm) |

|-------------|-------|-------|

| M1          | 12    | 0.36  |

| M2          | 120   | 0.36  |

| M3 - M5     | 12    | 0.36  |

| M6 - M9     | 12    | 0.36  |

| M10         | 120   | 0.36  |

| M11 -M20    | 12    | 0.36  |

| M21 - M24   | 1.44  | 0.36  |

Fig. 9 CMOS Realization of ZC-CDBA

Fig. 10 CMOS Realization of ZC-CDTA

The transistors used for positive feedback to reduce the P terminal input resistance are M10 and M11. The transistors used for positive feedback to reduce the N terminal input resistance are M3 and M4. The input terminal impedances formulas are given in Equations 6 and 7 [9-10].

$$r_{in-} = \frac{1}{g_{m1}g_{m3}} \left\{ \left( g_{ds1} + g_{m3} + g_{ds3} \right) - \frac{g_{m1}g_{m4}}{g_{ds4} + g_{m2} + g_{ds2}} \right\}$$

(6)

$$r_{in+} = \frac{1}{g_{m9}g_{m12}} \left\{ \left( g_{ds9} + g_{m12} + g_{ds12} \right) - \frac{g_{m9}g_{m11}}{g_{ds11} + g_{m10} + g_{ds10}} \right\}$$

(7)

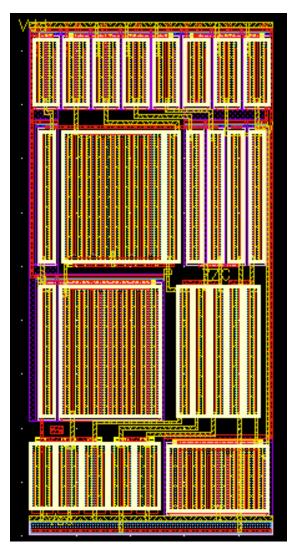

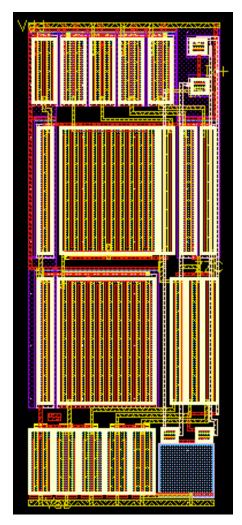

The layout of ZC-CDBA is given in Fig. 11. The size of the ZC-CDBA layout is 1070.19  $\mu m^2.$  The layout of ZC-CDTA is given in Fig. 12. The size of the ZC-CDTA layout is 844.71  $\mu m^2.$  All simulations are performed with the post-layout netlist.

Fig. 11 The layout of ZC-CDBA

Fig. 12 The layout of ZC-CDTA

## A. Impedance Characteristics of Amplifiers

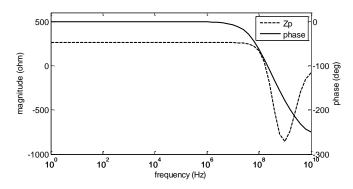

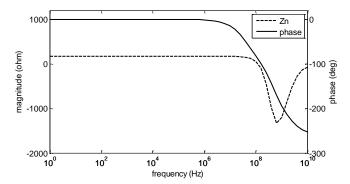

The input impedances of the P and N terminal are given in Fig. 13, 14, respectively. The input impedance values are much smaller than those in [9-10]. The biasing voltages;  $V_{b1}$ ,  $V_{b2}$ ,  $V_{b3}$  and  $V_{b4}$  voltages are selected as 500 mV, -400 mV, 100 mV and 300 mV, respectively. The  $I_b$  current is selected as  $30\mu A$ .

Fig. 13 Input impedance characteristic of terminal-P

Fig. 14 Input impedance characteristic of terminal-N

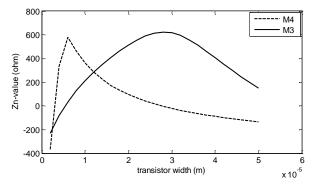

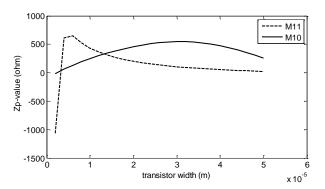

The effect of the M3 and M4 transistors to the N terminal input impedance is given in Fig. 15. The effect of the M10 and M11 transistors to the P terminal input impedance is also given in Fig. 16.

**Fig. 15** The effect of the M3 and M4 transistors' width to the N terminal input impedance

**Fig. 16** The effect of the M10 and M11 transistors' width to the P terminal input impedance

The phase margin values show that, the real part of the impedance values are positive until 1GHz frequency level for both P and N terminals. The desired input impedance level can be obtained by changing W/L ratios of these transistors.

It can be easily observed from Fig. 15, the input impedance is reduced by increasing the width of M3 and by decreasing the width of M4. From Fig. 16, the low input impedance is improved by increasing the width of M10 and by reducing the width of M11. From the figures, it can be derived that M4 and M11 transistors' width should be selected greater than  $12\mu m$ .

#### B. Stability and Worst Case Analysis of Amplifiers

Positive feedback is generally forbidden (except oscillator circuits) because of the stability problem. It is shown that, if used carefully, it is very effective for input impedance reduction.

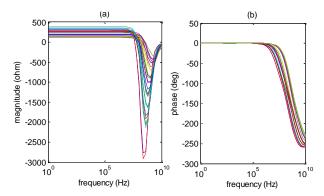

The worst case analysis for Zn and Zp are given in Fig. 17 and 18, respectively. The corner analyses are done for the input impedances of designed circuits to check its behaviors under various conditions of temperature and scattering of supply voltages. The fabrication conditions are selected with 3 parameters (ss, tt, ff). The temperature conditions are selected (-60°, 120°). The supply voltage conditions are selected ( $\pm 1.1 \text{ V}, \pm 0.9 \text{ V}$ ).

**Fig. 17** The impedance characteristics of terminal-N based on different corners (a) magnitude, (b) phase response

**Fig. 18** The impedance characteristics of terminal-P based on different corners (a) magnitude, (b) phase response

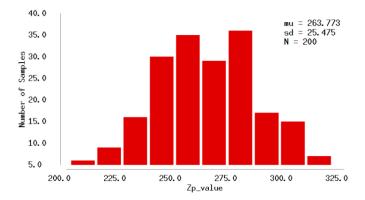

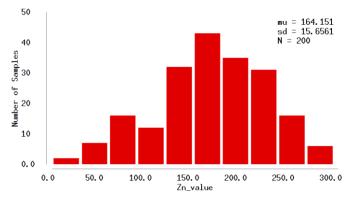

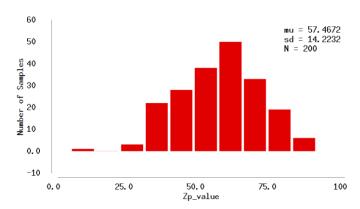

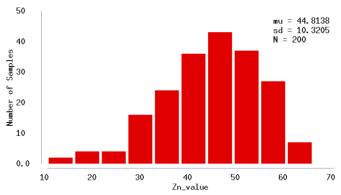

The system is stable for all different conditions of worst case parameters. The input impedance levels are chosen higher than the allowed minimum input impedance level to add more stability. For the proposed amplifiers, we select 263 Ohm and 164 Ohm input resistance values according to the worst case analysis for temperature (-60 C°, 120 C°), supply voltage ( $\pm 1.1$  V,  $\pm 0.9$ V), and process variations (change in transistor dimensions). This is illustrated in Fig. 19 and Fig. 20. We also show that impedance levels as low as  $45\Omega$  can be safely achieved by only considering process variations. This is illustrated in Fig. 21 and Fig. 22. All Monte Carlo analysis are performed for 200 samples.

**Fig. 19** Monte Carlo analysis for Zp used in this study

Fig. 20 Monte Carlo analysis for Zn used in this study

Fig. 21 Monte Carlo analysis for minimum achievable Zp

Fig. 22 Monte Carlo analysis for minimum achievable Zn

## C. Main Characteristics of ZC- CDBA and ZC-CDTA

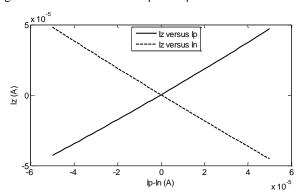

The Z terminal current characteristic for ZC-CDBA and ZC-CDTA is given in Fig. 23. The Z terminal current dynamic range is observed between -50 $\mu$ A- 50 $\mu$ A.

Fig. 23 The characteristic of Z terminal current versus to the P and N terminal currents

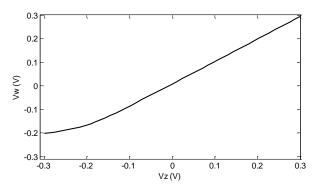

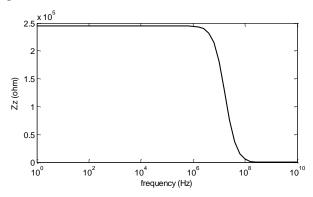

The voltage transfer characteristic of ZC-CDBA is given in Fig. 24. Z terminal output impedance for ZC-CDBA and ZC-CDTA are shown in Fig. 25. Fig. 26 shows the W terminal output impedance of ZC-CDBA. ZC-CDBA's W terminal voltage dynamic range is observed between 215mV, -215mV.

**Fig. 24** The characteristic of output terminal-W voltage versus to Z terminal voltage for ZC-CDBA

The output impedance at Z terminal is found as  $243k\Omega$ . The Z terminal output impedance value is enough to drive the load of the proposed applications. The W terminal output impedance is found as  $215\Omega$ .

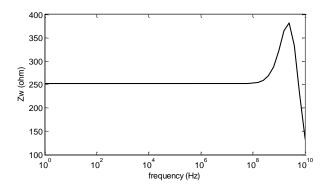

Fig. 25 The Z terminal output impedance

Fig. 26 The W terminal output impedance

The summary of the simulation results of the proposed ZC-CDBA is given in Table IV. Some performance parameters are also given for ZC-CDTA in Table V.

Note that f<sub>-3dB</sub> frequency for Iz/In and Iz/Ip are appropriate for the application circuits up to 150MHz cut-off frequency levels. The ZC-CDTA's X output terminals impedance level is observed as  $257k\Omega$ . This impedance level is also suitable for the proposed design examples.

TABLE IV PERFORMANCE OF 7C-CDBA

| TABLE IV PERFORMANCE OF ZC-CDBA                  |                                                  |  |  |  |

|--------------------------------------------------|--------------------------------------------------|--|--|--|

| Results                                          | Values                                           |  |  |  |

| Supply Voltage                                   | ±1 <b>V</b>                                      |  |  |  |

| Z terminal current dynamic range                 | $-50\mu A \le Iz \le 50\mu A$                    |  |  |  |

| W terminal voltage dynamic range                 | $-215 \text{mV} \le \text{Vw} \le 215 \text{mV}$ |  |  |  |

| f <sub>-3dB</sub> frequency for Iz/In            | 174.651MHz                                       |  |  |  |

| f <sub>-3dB</sub> frequency for Iz/Ip            | 238.849MHz                                       |  |  |  |

| P terminal input impedance                       | $263.773\Omega$                                  |  |  |  |

| N terminal input impedance                       | $164.151\Omega$                                  |  |  |  |

| Current gain (I <sub>z</sub> /I <sub>p,n</sub> ) | 1.015                                            |  |  |  |

| Voltage gain (V <sub>w</sub> /V <sub>z</sub> )   | 0.996                                            |  |  |  |

| W terminal output impedance                      | $214.674\Omega$                                  |  |  |  |

| Z terminal output impedance                      | $242.677 \mathrm{k}\Omega$                       |  |  |  |

| f <sub>-3dB</sub> frequency for Vw/Vz            | 243.432MHz                                       |  |  |  |

| Power Consumption                                | 1.58mW                                           |  |  |  |

| TABLE V PERFORMANCE OF ZC-CDTA          |                               |  |

|-----------------------------------------|-------------------------------|--|

| Results                                 | Values                        |  |

| Supply voltage                          | ±1 V                          |  |

| Power dissipation                       | 1.08 mW                       |  |

| Z terminal current dynamic range        | $-50\mu A \le Iz \le 50\mu A$ |  |

| f <sub>-3dB</sub> frequency for Iz/In   | 174.651MHz                    |  |

| f <sub>-3dB</sub> frequency for Iz/Ip   | 238.849MHz                    |  |

| P terminal input impedance              | $263.773\Omega$               |  |

| N terminal input impedance              | $164.151\Omega$               |  |

| Current gain $(I_z/I_{p,n})$            | 1.015                         |  |

| Z terminal output impedance             | $242.677 \mathrm{k}\Omega$    |  |

| g <sub>m</sub> (trans-conductance gain) | 51.773µS                      |  |

| X- terminal output impedance            | $256.480 \mathrm{k}\Omega$    |  |

| X+ terminal output impedance            | $256.480 \mathrm{k}\Omega$    |  |

## IV. DESIGN EXAMPLES

#### A. KHN Filter Based On ZC-CDBA

KHN filter structure is one of the widely used filter structures in analog signal processing. KHN filter was

proposed by Kerwin, Huelsman, and Newcomb using statevariable synthesis in 1967. It has also been produced commercially.

The most important characteristic of the KHN filter transfer function is the adequacy for different type of filter implementation (band pass, high pass, low pass) at the same time. Another important property of KHN filter is the conformity for low sensitivity realization.

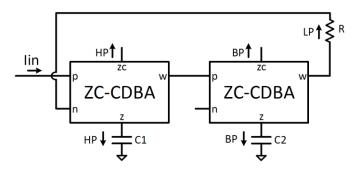

The proposed application circuit employing two ZC-CDBAs and three passive elements is given in Fig. 27. The proposed filter is the developed version those in [14]. The circuit of the KHN filter has two band pass filter sections, two high pass filter sections and one low pass filter section. One of the high pass filter sections has high impedance. The grounded capacitors C<sub>1</sub> and C<sub>2</sub> are selected as 200fF. The resistor value is selected as  $R=800\Omega$ . The capacitors and resistor values are selected to provide 100MHz center frequency. The performance of the current differencing unit with positive feedback is verified with KHN filter.

Fig. 27 ZC-CDBA filter application

The routine node analyses of the proposed topology yield the following transfer functions for high-pass, band-pass, lowpass filter given in Equations 8, 9, 10, respectively. The pole angular frequency  $\omega_0$  and the quality factor Q are given in Equation 11.

$$\frac{I_{HP}}{I_{IN}} = \frac{s^2}{s^2 + s\frac{1}{C_1} + \frac{G}{C_1C_2}} \tag{8}$$

$$\frac{I_{BP}}{I_{IN}} = \frac{s\frac{1}{C_1}}{s^2 + s\frac{1}{C_1} + \frac{G}{C_1C_2}}$$

(9)

$$\frac{I_{LP}}{I_{IN}} = \frac{\frac{G}{C_1 C_2}}{s^2 + s \frac{1}{C_1} + \frac{G}{C_1 C_2}}$$

(10)

$$\omega_0 = \sqrt{\frac{G}{C_1 C_2}}, \ Q = \sqrt{\frac{GC_1}{C_2}}$$

(11)

Sensitivity analyses of the proposed filter with respect to active and passive components yield the following Equations 12, 13, respectively.

$$S_G^{W_0} = -S_{C_1}^{W_0} = -S_{C_2}^{W_0} = 0.5 (12)$$

$$S_G^Q = S_{C_1}^Q = -S_{C_2}^Q = 0.5 (13)$$

The sensitivity values are satisfactorily very small. Therefore, the proposed filter configuration enjoys low sensitivity performance. To obtain filter characteristics, layout and post-layout simulations are done for proposed circuits.

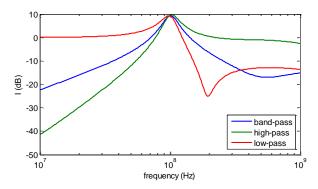

The post-layout simulated responses of low-pass, band-pass, high-pass filters are given in Fig. 28. The post-layout simulations are in a good agreement with the schematic versions. The KHN filter can operate up to 100MHz.

Fig. 28 The gain-frequency responses of the proposed KHN filter

## B. An Electronically Controllable Filter Using ZC-CDTA

A special radio communication system known as software-defined radio (SDR) are performed by means of software on a personal computer or embedded system in contrast to typical hardware components (e.g. mixers, filters, amplifiers, modulators/demodulators, detectors, etc.). SDR characteristics as frequency, band-widths, modulation, etc. can be controllable and used as "computer tools" (software, RAM programmed, etc.). Also, cognitive radio (CR) is a different version of the software defined radio [15].

It is compulsory to catch different frequency by using designed hardware systems for some applications. For example, it is inevitable to implement the different positioning system protocols (GPS, GLONASS, Beidou, GNSS and Galileo) in the same chip. A reconfigurable receiver can be adapted different frequency [16].

The Z copied current differencing trans-conductance

amplifier biquadratic filter structure is given in Fig. 29. The high-pass filter transfer function, band-pass filter transfer function, low-pass filter transfer function, the pole angular frequency  $\omega_0$  and the quality factor Q are given in Equations 14, 15, 16, 17, 18, respectively.

$$\frac{I_{HP}}{I_{IN}} = \frac{C_1 C_2 s^2}{g_{m1} g_{m2} + C_2 g_{m1} s + C_1 C_2 s^2}$$

(14)

$$\frac{I_{BP}}{I_{IN}} = \frac{C_2 g_{m1} s}{g_{m1} g_{m2} + C_2 g_{m1} s + C_1 C_2 s^2}$$

(15)

$$\frac{I_{LP}}{I_{IN}} = \frac{g_{m1}g_{m2}}{g_{m1}g_{m2} + C_2g_{m1}s + C_1C_2s^2}$$

(16)

$$\omega_0 = \sqrt{\frac{g_{m1}g_{m2}}{C_1C_2}} \tag{17}$$

$$Q = \sqrt{\frac{g_{m2}C_1}{g_{m1}C_2}}$$

(18)

Fig. 29 ZC-CDTA biquadratic filter structure [17]

The sensitivities with respect to active and passive components are not larger than absolute value of 0.5.

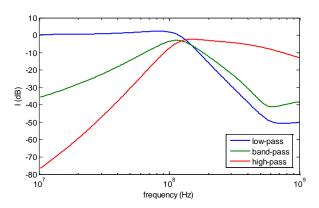

The post-layout simulations for the biquadratic filter structure are shown in Fig. 30.

**Fig. 30** The gain-frequency responses of the biquadratic filter output

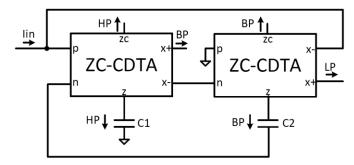

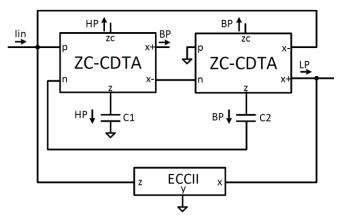

The basic biquadratic filter structure is modified by using electronically controllable second generation current conveyor to obtain reconfigurable filter structure. The improved filter structure is shown in Fig. 31. The new band pass function of the filter is given in Equation 19.

$$\frac{I_{BP}}{I_E} = \frac{\frac{C_2 g_{m1} s}{(1 - A g_{m1} g_{m2})}}{1 + \frac{C_2 g_{m1} s}{(1 - A g_{m1} g_{m2})} + \frac{C_1 C_2 s^2}{(1 - A g_{m1} g_{m2})}}$$

(19)

The gain at  $f_0$  of the band pass output does not change as before GBP = 1. The center frequency and the quality factor of the new filter structure are given in Equation 20, 21, respectively.

$$\omega_0 = \frac{(1 - Ag_{m1}g_{m2})}{2\pi\sqrt{C_1C_2}} \tag{20}$$

$$Q = \sqrt{(1 - Ag_{m1}g_{m2})} \frac{\sqrt{C_1 C_2}}{C_2 g_{m1}}$$

(21)

The quality factor and the center frequency of the controllable filter can be adjusted by the aid of current ratio (A) of the electronically controllable second generation current conveyor given in Fig. 31. The capacitance values are selected as C1 = C2 = 200 fF. The CMOS structure and the performance parameters of the ECCII are chosen as the same values those in [18]. In this work the performance of the current differencing unit with positive feedback is tested with reconfigurable filter structure.

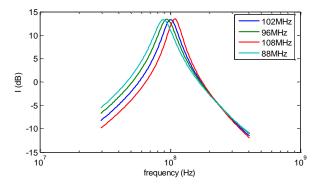

The capacitance values are selected according to the suitable frequency range for positioning systems protocols (GPS, GLONASS, Beidou, GNSS and Galileo). The center frequency of band pass filter 88 MHz, 96 MHz, 102 MHz and 108 MHz are obtained for bias current  $I_A=22~\mu A,\ 16~\mu A,\ 10~\mu A,\ 5~\mu A$  respectively. The  $I_C,\ I_B$  bias currents of ECCII are selected as  $60~\mu A.$

**Fig. 31** The electronically controllable filter using ZC-CDTA [18]

Fig. 32 shows the band pass output for different current ratio of the electronically controllable second generation current conveyor. The agile filter output is also appropriate for FM frequency range for receiver applications. The operating frequency of the biquadratic and frequency agile filter is

improved up to 100MHz compared those in [17-18].

Fig. 32 The reconfigurable filter output

#### V. CONCLUSION

The conventional wisdom is that analog circuits should not include positive feedback loops. As controversial as it seems, positive feedback is successfully used for impedance improvement in this study. With adding few transistors very low input resistance values are achieved for current amplifiers. Stability analysis is also performed and it is shown that input resistance values as low as 50  $\Omega$  can safely be implemented.

The proposed amplifiers ZC-CDBA and ZC-CDTA are simulated using post-layout parameters in Cadence environment. The size of the ZC-CDBA layout is  $1070.19 \ \mu m^2$ ; the size of the ZC-CDTA layout is  $844.71 \mu m^2$ . AMS  $0.18 \mu m$  transistor parameters are used in the simulations.

The proposed current amplifiers are also tested in filter applications. A new KHN and electronically controllable filter configurations are proposed. The total harmonic distortion of the KHN and frequency agile filters are measured with applied  $100\mu A$  sine wave at 100MHz. The distortions are smaller than 5%. It is shown that the filters operate accurately to the frequency level of 100MHz. These are the clear signs of the proposed amplifiers' high performance.

## REFERENCES

- [1] C. Toumazou, F. Lidjey, D. Haigh, Analog IC Design: The Current-Mode Approach, Exeter, UK, Peter Peregrinus, 1990.

- [2] B. Wilson, "Trend in current conveyor and current-mode amplifier design," Int. J. Electron., Vol. 23, pp. 573-583,1992.

- [3] D. Biolek, R. Senani, V. Biolková, Z. Kolka," Active Elements for Analog Signal Processing: Classification, Review, and New Proposals", RADIOENGINEERING, VOL. 17, NO. 4, , pp.15-32. DECEMBER 2008.

- [4] Dalibor Biolek, Josef Bajer, Viera Biolková, Zdeněk Kolka, Michal Kubíček, 'Z Copy Controlled Gain Current Differencing Buffered Amplifier and its applications' Int. Journal of Circuit Theory and Applications, vol. 39, no. 3, pp. 257-274, 2011.

- [5] C. Acar, S. Ozoguz, A versatile building block: current differencing buffered amplifier suitable for analog signal processing filters. Microelectron J 1999;30:157–60.

- [6] F. Kacar, H. Kuntman, "A New Improved CMOS Realization of CDTA and Its Filter Application", Turk J Elec Eng & Comp Sci, Vol.19, No.4, 2011.

- [7] A. Uygur, H. Kuntman, 'Seventh order elliptic video filter with 0.1dB pass band ripple employed CMOS CDTAs', AEU: International Journal of Electronics and Communications, Vol.61, 320-328, 2007.

- [8] A. Fabre, 'Third generation current conveyor: a new active element' Electronics Letters 1995; 31: 338-339.

- [9] M. Altun, H. Kuntman, 'Design of a Fully Differential Current Mode Operational Amplifier with Improved Input-Output Impedances and Its Filter Applications', AEU: International Journal of Electronics and Communications, Vol.62, No. 3, 239-244, 2008.

- [10] M. Altun, 'Design of a Current Mode Operational Amplifier and Its Applications', M.Sc Thesis, İstanbul Technical University, Institute of Science and Technology, Turkey, 2007.

- [11] G. Palmisano, G. Palumbo, S. Pennisi, 'CMOS current amplifiers', Boston MA:Kluwer Academic Publishers, 1999.

- [12] R. S. Assaad, J. Silva-Martinez, "The Recycling Folded Cascode: A General Enhancement of the Folded Cascode Amplifier," Solid-State Circuits, IEEE Journal of, vol.44, no.9, pp.2535,2542, Sept. 2009.

- [13] A. Arbel, L. Goldminz, 'Output stage for current-feedback amplifiers, theory and applications', Analog

- Integrated Circuits and Signal Processing 1992; 2: 243-255.

- [14] E. Alaybeyoğlu, A. Güney, M. Altun, H. Kuntman, "Low Input Impedance Current Differencing Unit for Current Mode Active Devices Improved by Positive Feedback and ZC-CDBA Filter Application", Proc. of ELECO 2013: The 8th International Conference on Electrical and Electronics Engineering, pp.26-30, 28-30 November 2013, Bursa, TURKEY.

- [15] Y. Lakys, B. Godara, A. Fabre, "Cognitive and encrypted communications: state of the art and a new approach for frequency agile filters", Turk J Elec Eng & Comp Sci, Vol.19, No.2, 2011.

- [16] E. Armağan, H. Kuntman, "Design of balanced differential pair based CCCII circuit and configurable frequency agile filter application in 28nm process", Proc. of ELECO '2012: Conference on Electrical and Electronics Engineering, 29 November - 01 December 2012, Bursa, Turkey: pp. 257-261.

- [17] E. Alaybeyoğlu, H. Kuntman, "A New CMOS ZC-CDTA Realization and Its Filter Applications", accepted for publication in TJEECS: Turkish Journal of Electrical Engineering & Computer Sciences (ELK-1305-262).

- [18] E. Alaybeyoğlu, "Analog circuit design with new active circuit components", M.Sc. Thesis, Istanbul Technical University, Istanbul, Graduate School of Science Engineering and Technology, Turkey, 2013.