Main Page

From The Emerging Circuits and Computation Group at ITU

(Difference between revisions)

| (14 intermediate revisions by one user not shown) | |||

| Line 24: | Line 24: | ||

| style="padding:2px;" | <h2 id="mp-tafi-h2" style="margin:3px; background:#8FBC8F; font-size:125%; font-weight:bold; border:1px solid #3CB371; text-align:left; color:#000; padding:0.2em 0.4em;">Group news</h2> | | style="padding:2px;" | <h2 id="mp-tafi-h2" style="margin:3px; background:#8FBC8F; font-size:125%; font-weight:bold; border:1px solid #3CB371; text-align:left; color:#000; padding:0.2em 0.4em;">Group news</h2> | ||

| + | |||

| + | * <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> Nov. 2018</span> We will present our work "''Realization of Four-Terminal Switching Lattices: Technology Development and Circuit Modeling''" in a premier conference on electronic design automation [http://www.date-conference.com/ DATE 2019]. | ||

| + | |||

| + | * <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> Nov. 2018</span> We will present our work "''A Satisfiability-Based Approximate Algorithm for Logic Synthesis Using Switching Lattices''" in a premier conference on electronic design automation [http://www.date-conference.com/ DATE 2019]. | ||

* <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> June 2018</span> We will present our work "''Integrated Synthesis Methodology for Crossbar Arrays''" in a leading conference on nanocircuits/nanoarchitectures [http://www.nanoarch.org IEEE/ACM-NANOARCH 2018]. | * <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> June 2018</span> We will present our work "''Integrated Synthesis Methodology for Crossbar Arrays''" in a leading conference on nanocircuits/nanoarchitectures [http://www.nanoarch.org IEEE/ACM-NANOARCH 2018]. | ||

| Line 40: | Line 44: | ||

* <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> Aug. 2017</span> Our two papers in the area of ''fault tolerance for nano-crossbar arrays'' are accepted in journals [http://csur.acm.org/ CSUR] and [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6245516 TETC] having impact factors of 6,8 and 3,8. This endorses our leading expertise in this area. | * <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> Aug. 2017</span> Our two papers in the area of ''fault tolerance for nano-crossbar arrays'' are accepted in journals [http://csur.acm.org/ CSUR] and [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6245516 TETC] having impact factors of 6,8 and 3,8. This endorses our leading expertise in this area. | ||

| − | |||

| − | |||

| − | |||

| − | |||

<div class="toccolours mw-collapsible mw-collapsed" cellspacing="0" cellpadding="0" width=100% style="border:1px solid #3CB371; padding:1px;"> | <div class="toccolours mw-collapsible mw-collapsed" cellspacing="0" cellpadding="0" width=100% style="border:1px solid #3CB371; padding:1px;"> | ||

:<u>'''PREVIOUS NEWS'''</u>: | :<u>'''PREVIOUS NEWS'''</u>: | ||

<div class="mw-collapsible-content"> | <div class="mw-collapsible-content"> | ||

| + | |||

| + | * <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> July 2017</span> Our project on ''approximate computing and applications in image processing with learning'' received a grant from the TUBITAK Scientific and Technological Research Projects Funding Program (1001). | ||

| + | |||

| + | * <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> June 2017</span> We place first in [http://www.istanbul.emo.org.tr/ graduation project competition - 2017] launched by the Chamber of Electrical Engineers of Turkey (EMO); our project is titled "''Implementation of a Fault-Aware 8-Bit Reversible Microprocessor''". | ||

* <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> May 2017</span> We will present our work "''A Power Efficient System Design Methodology Employing Approximate Arithmetic Units''" in [http://www.isvlsi.org/ IEEE-ISVLSI 2017]. | * <span style="background:#8FBC8F; color:#FFFFFF; font-size: 100%; border:1px solid #3CB371;"> May 2017</span> We will present our work "''A Power Efficient System Design Methodology Employing Approximate Arithmetic Units''" in [http://www.isvlsi.org/ IEEE-ISVLSI 2017]. | ||

| Line 141: | Line 145: | ||

* Various funded research projects available for '''graduate''' and '''undergraduate''' students on the following topics: | * Various funded research projects available for '''graduate''' and '''undergraduate''' students on the following topics: | ||

| − | ** Circuit design | + | ** Circuit design for emerging technologies based on crossbar arrays |

| − | ** Stochastic | + | ** Stochastic, bit stream, and time based computing |

** Reliability of electronic circuits and systems | ** Reliability of electronic circuits and systems | ||

| + | ** Approximate computing | ||

** Reversible circuit design | ** Reversible circuit design | ||

| − | ** | + | ** Large-area electronics |

<h2 id="mp-itn-h2" style="margin:3px; background:#BC8F9F; font-size:125%; font-weight:bold; border:1px solid #BA55D3; text-align:left; color:#000; padding:0.2em 0.4em;">Collaborating with our group</h2> | <h2 id="mp-itn-h2" style="margin:3px; background:#BC8F9F; font-size:125%; font-weight:bold; border:1px solid #BA55D3; text-align:left; color:#000; padding:0.2em 0.4em;">Collaborating with our group</h2> | ||

* We are wide open to '''national/international collaborations''' with academia and industry. | * We are wide open to '''national/international collaborations''' with academia and industry. | ||

| − | * We are dedicated to establish new partnerships for | + | * We are dedicated to establish new partnerships for [http://ec.europa.eu/programmes/horizon2020/ '''EU H2020'''] work programmes including, but not limited to: |

** Future and Emerging Technologies ([http://ec.europa.eu/programmes/horizon2020/en/h2020-section/future-and-emerging-technologies FET]) | ** Future and Emerging Technologies ([http://ec.europa.eu/programmes/horizon2020/en/h2020-section/future-and-emerging-technologies FET]) | ||

| − | ** Information and Communication Technologies ([http://ec.europa.eu/digital-agenda/en/information-communication-technologies-horizon-2020 ICT]) | + | ** Information and Communication Technologies ([http://ec.europa.eu/digital-agenda/en/information-communication-technologies-horizon-2020 ICT]), especially for [http://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/ict-06-2019.html ICT-06] |

| − | ** Cluster for Application and Technology Research in Europe on NanoElectronics ([http://www.catrene.org/index.php CATRENE]) | + | <!--** Cluster for Application and Technology Research in Europe on NanoElectronics ([http://www.catrene.org/index.php CATRENE]) |

| − | ** The projects needed expertise in reliability, circuit design, and electronic design automation | + | ** The projects needed expertise in reliability, circuit design, and electronic design automation --> |

| − | + | * We are dedicated to establish new partnerships within [http://ec.europa.eu/programmes/horizon2020/ '''EU Cost'''] actions and [http://www.tubitak.gov.tr/tr/uluslararasi/ikili-proje-destekleri/icerik-basvuruya-acik-programlar '''joint international'''] calls. | |

| + | * We are also interested in industry based and market driven partnerships through [http://www.eurekanetwork.org/ '''EUREKA''']. | ||

[[Image:Funding-7.png|center|none|450px|link=http://www.ecc.itu.edu.tr/index.php?title=Projects]] | [[Image:Funding-7.png|center|none|450px|link=http://www.ecc.itu.edu.tr/index.php?title=Projects]] | ||

| Line 170: | Line 176: | ||

<div><center> | <div><center> | ||

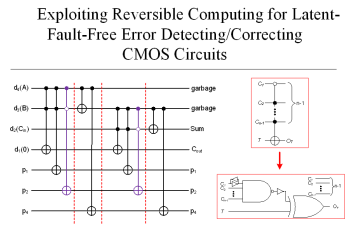

| − | <li style="display: inline-block;"> [[File:Main-pub- | + | <li style="display: inline-block;"> [[File:Main-pub-5-2018.png|link=http://www.ecc.itu.edu.tr/images/7/7d/Altun_Parvin_Cilasun_Exploiting_Reversible_Computing_for_CMOS_Fault_Tolerance.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/7/7d/Altun_Parvin_Cilasun_Exploiting_Reversible_Computing_for_CMOS_Fault_Tolerance.pdf The paper] published in [http://ieeeaccess.ieee.org/ IEEE Access], 2018]] |

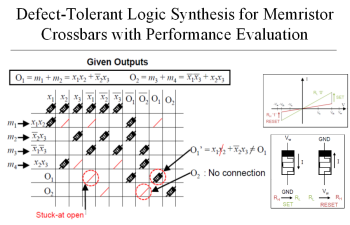

| − | <li style="display: inline-block;"> [[File:Main-pub- | + | <li style="display: inline-block;"> [[File:Main-pub-4-2018.png|link=http://www.ecc.itu.edu.tr/images/d/db/Tunali_Morgul_Altun_Defect_Tolerant_Memristor_Crossbars.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/d/db/Tunali_Morgul_Altun_Defect_Tolerant_Memristor_Crossbars.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=40 IEEE Micro], 2018]] |

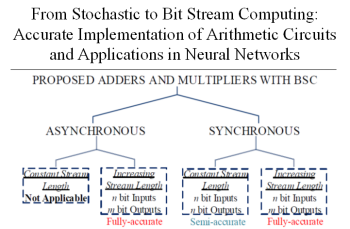

| + | <li style="display: inline-block;"> [[File:Main-pub-3-2018.png|link=http://www.ecc.itu.edu.tr/images/7/73/Vahapoglu_Altun_From_Stochastic_To_Bit_Stream_Computing.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/7/73/Vahapoglu_Altun_From_Stochastic_To_Bit_Stream_Computing.pdf The paper] published in [http://arxiv.org/abs/1805.06262 arXiv], 2018]] | ||

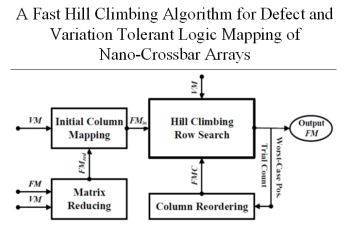

<li style="display: inline-block;"> [[File:Main-pub-2-2018.png|link=http://www.ecc.itu.edu.tr/images/7/71/Peker_Altun_Variation_Tolerant_Logic_Mapping_of_Nano_Crossbars.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/7/71/Peker_Altun_Variation_Tolerant_Logic_Mapping_of_Nano_Crossbars.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6687315 IEEE TMSCS], 2018]] | <li style="display: inline-block;"> [[File:Main-pub-2-2018.png|link=http://www.ecc.itu.edu.tr/images/7/71/Peker_Altun_Variation_Tolerant_Logic_Mapping_of_Nano_Crossbars.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/7/71/Peker_Altun_Variation_Tolerant_Logic_Mapping_of_Nano_Crossbars.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6687315 IEEE TMSCS], 2018]] | ||

| + | |||

| + | <!-- | ||

| + | <li style="display: inline-block;"> [[File:Main-pub-1-2018.png|link=http://www.ecc.itu.edu.tr/images/5/57/Tunali_Altun_Logic_Synthesis_and_Defect_Tolerance_for_Memristive_Crossbars.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/5/57/Tunali_Altun_Logic_Synthesis_and_Defect_Tolerance_for_Memristive_Crossbars.pdf The paper] presented at [http://www.date-conference.com/ DATE], 2018]] | ||

<li style="display: inline-block;"> [[File:Main-pub-1.png|link=http://www.ecc.itu.edu.tr/images/c/cc/Tunali_Altun_Permanent_and_Transient_Fault_Tolerance_for_Reconfigurable_Nano-Crossbar_Arrays.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/c/cc/Tunali_Altun_Permanent_and_Transient_Fault_Tolerance_for_Reconfigurable_Nano-Crossbar_Arrays.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=43 IEEE TCAD], 2017]] | <li style="display: inline-block;"> [[File:Main-pub-1.png|link=http://www.ecc.itu.edu.tr/images/c/cc/Tunali_Altun_Permanent_and_Transient_Fault_Tolerance_for_Reconfigurable_Nano-Crossbar_Arrays.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/c/cc/Tunali_Altun_Permanent_and_Transient_Fault_Tolerance_for_Reconfigurable_Nano-Crossbar_Arrays.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=43 IEEE TCAD], 2017]] | ||

| − | + | <li style="display: inline-block;"> [[File:Main-pub-3.png|link=http://www.ecc.itu.edu.tr/images/1/16/Altun_Comert_A_Change-Point_based_Reliability_Prediction_Model_using_Field_Return_Data.pdf|thumb|none|412px|[http://www.ecc.itu.edu.tr/images/1/16/Altun_Comert_A_Change-Point_based_Reliability_Prediction_Model_using_Field_Return_Data.pdf The paper] published in [http://www.journals.elsevier.com/reliability-engineering-and-system-safety RESS], 2016]] | |

<li style="display: inline-block;"> [[File:Main-pub-1-2017.png|link=http://www.ecc.itu.edu.tr/images/b/b4/Ayhan_Kula_Altun_Approximate_System_Design_Methodology.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/b/b4/Ayhan_Kula_Altun_Approximate_System_Design_Methodology.pdf The paper] presented at [http://www.isvlsi.org/ IEEE-ISVLSI], 2017]] | <li style="display: inline-block;"> [[File:Main-pub-1-2017.png|link=http://www.ecc.itu.edu.tr/images/b/b4/Ayhan_Kula_Altun_Approximate_System_Design_Methodology.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/b/b4/Ayhan_Kula_Altun_Approximate_System_Design_Methodology.pdf The paper] presented at [http://www.isvlsi.org/ IEEE-ISVLSI], 2017]] | ||

<li style="display: inline-block;"> [[File:Main-pub-2.png|link=http://www.ecc.itu.edu.tr/images/c/cd/Susam_Altun_Fast_Synthesis_of_Reversible_Circuits_using_a_Sorting_Algorithm_and_Optimization.pdf|thumb|none|330px|[http://www.ecc.itu.edu.tr/images/c/cd/Susam_Altun_Fast_Synthesis_of_Reversible_Circuits_using_a_Sorting_Algorithm_and_Optimization.pdf The paper] published in [http://www.oldcitypublishing.com/journals/mvlsc-home/ MVLSC], 2017]] | <li style="display: inline-block;"> [[File:Main-pub-2.png|link=http://www.ecc.itu.edu.tr/images/c/cd/Susam_Altun_Fast_Synthesis_of_Reversible_Circuits_using_a_Sorting_Algorithm_and_Optimization.pdf|thumb|none|330px|[http://www.ecc.itu.edu.tr/images/c/cd/Susam_Altun_Fast_Synthesis_of_Reversible_Circuits_using_a_Sorting_Algorithm_and_Optimization.pdf The paper] published in [http://www.oldcitypublishing.com/journals/mvlsc-home/ MVLSC], 2017]] | ||

| Line 190: | Line 200: | ||

<div><center> | <div><center> | ||

| + | <li style="display: inline-block;"> [[File:Altun_Birthday-2018.jpg|link=http://www.ecc.itu.edu.tr/index.php?title=People|thumb|none|380px|Birthday party, 2018]] | ||

<li style="display: inline-block;"> [[File:ECC_showup_2017.jpg|link=http://www.ecc.itu.edu.tr/index.php?title=People|thumb|none|380px|ECC show up, 2017]] | <li style="display: inline-block;"> [[File:ECC_showup_2017.jpg|link=http://www.ecc.itu.edu.tr/index.php?title=People|thumb|none|380px|ECC show up, 2017]] | ||

<li style="display: inline-block;"> [[File:ECC_iftar_2016.jpg|link=http://www.ecc.itu.edu.tr/index.php?title=People|thumb|none|380px|ECC having iftar in Baltalimani, 2016]] | <li style="display: inline-block;"> [[File:ECC_iftar_2016.jpg|link=http://www.ecc.itu.edu.tr/index.php?title=People|thumb|none|380px|ECC having iftar in Baltalimani, 2016]] | ||

<li style="display: inline-block;"> [[File:ECC_grup_foto_3.jpg|link=http://www.ecc.itu.edu.tr/index.php?title=People|thumb|none|380px|Group dining in Baltalimani, 2015]] | <li style="display: inline-block;"> [[File:ECC_grup_foto_3.jpg|link=http://www.ecc.itu.edu.tr/index.php?title=People|thumb|none|380px|Group dining in Baltalimani, 2015]] | ||

| − | <!-- <li style="display: inline-block;"> [[File:ECC_grup_foto_2.jpg|link=http://www.ecc.itu.edu.tr/index.php?title=People|thumb|none|380px|ECC show up, 2015]] | + | <!-- <li style="display: inline-block;"> [[File:ECC_grup_foto_2.jpg|link=http://www.ecc.itu.edu.tr/index.php?title=People|thumb|none|380px|ECC show up, 2015]] |

<li style="display: inline-block;"> [[File:ECC_grup_foto_1.jpg|link=http://www.ecc.itu.edu.tr/index.php?title=People|thumb|none|380px|Group meeting with pizza, 2014]] | <li style="display: inline-block;"> [[File:ECC_grup_foto_1.jpg|link=http://www.ecc.itu.edu.tr/index.php?title=People|thumb|none|380px|Group meeting with pizza, 2014]] | ||

| − | + | <li style="display: inline-block;"> [[File:ECC_ofis_foto_1.jpg|link=http://www.ecc.itu.edu.tr/index.php?title=People|thumb|none|360px|Our office space, 2015]] --> | |

</center></div> | </center></div> | ||

Revision as of 16:08, 21 November 2018

Welcome to the Emerging Circuits and Computation (ECC) Group | |

|

Our group, comprised of Mustafa Altun and his scholars & students, is in the Department of Electronics and Communication Engineering at Istanbul Technical University. In terms of research, we aim to develop electronic design automation (EDA) and circuit design techniques for emerging nanotechnologies and new computing paradigms. We also have a special interest in electronics reliability in both circuit and system levels. In terms of teaching, we offer courses on digital/analog circuit design as well as on computational nanoelectronics.  | |

|

|

|

Selected recent publications |

Group pictures |