Main Page

From The Emerging Circuits and Computation Group at ITU

(Difference between revisions)

| (3 intermediate revisions by one user not shown) | |||

| Line 147: | Line 147: | ||

** Reversible circuit design | ** Reversible circuit design | ||

** Large-area electronics | ** Large-area electronics | ||

| − | |||

<h2 id="mp-itn-h2" style="margin:3px; background:#BC8F9F; font-size:125%; font-weight:bold; border:1px solid #BA55D3; text-align:left; color:#000; padding:0.2em 0.4em;">Collaborating with our group</h2> | <h2 id="mp-itn-h2" style="margin:3px; background:#BC8F9F; font-size:125%; font-weight:bold; border:1px solid #BA55D3; text-align:left; color:#000; padding:0.2em 0.4em;">Collaborating with our group</h2> | ||

| Line 156: | Line 155: | ||

<!--** Cluster for Application and Technology Research in Europe on NanoElectronics ([http://www.catrene.org/index.php CATRENE]) | <!--** Cluster for Application and Technology Research in Europe on NanoElectronics ([http://www.catrene.org/index.php CATRENE]) | ||

** The projects needed expertise in reliability, circuit design, and electronic design automation --> | ** The projects needed expertise in reliability, circuit design, and electronic design automation --> | ||

| − | * We are dedicated to establish new | + | * We are dedicated to establish new partnerships within [http://ec.europa.eu/programmes/horizon2020/ '''EU Cost'''] actions and [http://www.tubitak.gov.tr/tr/uluslararasi/ikili-proje-destekleri/icerik-basvuruya-acik-programlar '''joint international'''] calls. |

* We are also interested in industry based and market driven partnerships through [http://www.eurekanetwork.org/ '''EUREKA''']. | * We are also interested in industry based and market driven partnerships through [http://www.eurekanetwork.org/ '''EUREKA''']. | ||

[[Image:Funding-7.png|center|none|450px|link=http://www.ecc.itu.edu.tr/index.php?title=Projects]] | [[Image:Funding-7.png|center|none|450px|link=http://www.ecc.itu.edu.tr/index.php?title=Projects]] | ||

| Line 173: | Line 172: | ||

<div><center> | <div><center> | ||

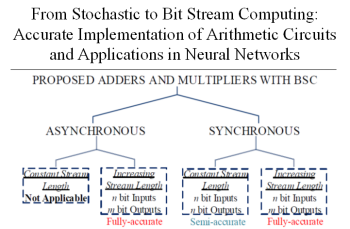

| − | <li style="display: inline-block;"> [[File:Main-pub-3-2018.png|link=http://www.ecc.itu.edu.tr/images/7/73/Vahapoglu_Altun_From_Stochastic_To_Bit_Stream_Computing.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/7/73/Vahapoglu_Altun_From_Stochastic_To_Bit_Stream_Computing.pdf The paper] published in [http://arxiv.org/abs/1805.06262 arXiv | + | <li style="display: inline-block;"> [[File:Main-pub-3-2018.png|link=http://www.ecc.itu.edu.tr/images/7/73/Vahapoglu_Altun_From_Stochastic_To_Bit_Stream_Computing.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/7/73/Vahapoglu_Altun_From_Stochastic_To_Bit_Stream_Computing.pdf The paper] published in [http://arxiv.org/abs/1805.06262 arXiv], 2018]] |

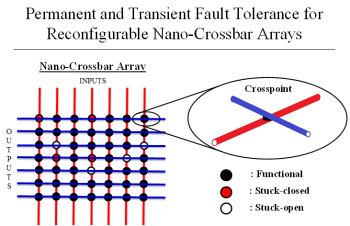

<li style="display: inline-block;"> [[File:Main-pub-1-2018.png|link=http://www.ecc.itu.edu.tr/images/5/57/Tunali_Altun_Logic_Synthesis_and_Defect_Tolerance_for_Memristive_Crossbars.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/5/57/Tunali_Altun_Logic_Synthesis_and_Defect_Tolerance_for_Memristive_Crossbars.pdf The paper] presented at [http://www.date-conference.com/ DATE], 2018]] | <li style="display: inline-block;"> [[File:Main-pub-1-2018.png|link=http://www.ecc.itu.edu.tr/images/5/57/Tunali_Altun_Logic_Synthesis_and_Defect_Tolerance_for_Memristive_Crossbars.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/5/57/Tunali_Altun_Logic_Synthesis_and_Defect_Tolerance_for_Memristive_Crossbars.pdf The paper] presented at [http://www.date-conference.com/ DATE], 2018]] | ||

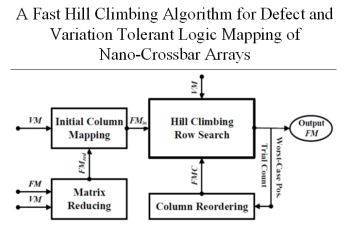

<li style="display: inline-block;"> [[File:Main-pub-2-2018.png|link=http://www.ecc.itu.edu.tr/images/7/71/Peker_Altun_Variation_Tolerant_Logic_Mapping_of_Nano_Crossbars.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/7/71/Peker_Altun_Variation_Tolerant_Logic_Mapping_of_Nano_Crossbars.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6687315 IEEE TMSCS], 2018]] | <li style="display: inline-block;"> [[File:Main-pub-2-2018.png|link=http://www.ecc.itu.edu.tr/images/7/71/Peker_Altun_Variation_Tolerant_Logic_Mapping_of_Nano_Crossbars.pdf|thumb|none|350px|[http://www.ecc.itu.edu.tr/images/7/71/Peker_Altun_Variation_Tolerant_Logic_Mapping_of_Nano_Crossbars.pdf The paper] published in [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6687315 IEEE TMSCS], 2018]] | ||

Revision as of 09:28, 19 September 2018

Welcome to the Emerging Circuits and Computation (ECC) Group | |

|

Our group, comprised of Mustafa Altun and his scholars & students, is in the Department of Electronics and Communication Engineering at Istanbul Technical University. In terms of research, we aim to develop electronic design automation (EDA) and circuit design techniques for emerging nanotechnologies and new computing paradigms. We also have a special interest in electronics reliability in both circuit and system levels. In terms of teaching, we offer courses on digital/analog circuit design as well as on computational nanoelectronics.  | |

|

|

|

Selected recent publications |

Group pictures |