Araştırma

| Line 142: | Line 142: | ||

|- valign="top" | |- valign="top" | ||

| '''kurum & program''': | | '''kurum & program''': | ||

| − | | [http://tubitak.gov.tr/tr/burslar/lisans/burs-programlari/2209-a TÜBİTAK Üniversite Öğrencileri Yurt İçi Araştırma Projeleri Destek Programı (2209/A)] | + | | [http://www.tubitak.gov.tr/tr/burslar/lisans/burs-programlari/icerik-2209-a-universite-ogrencileri-yurt-ici-arastirma-projeleri-destek-p TÜBİTAK Üniversite Öğrencileri Yurt İçi Araştırma Projeleri Destek Programı (2209/A)] |

|- valign="top" | |- valign="top" | ||

| '''süre''': | | '''süre''': | ||

Revision as of 01:07, 27 August 2015

Araştırmalarımızın amacı, elektronik devre ve sistemler için hesaplama, devre tasarımı ve güvenilirlik konularında yeni yaklaşımlar geliştirmektir. Araştırmalarımız temelde yeni ve gelişen teknolojileri hedef almaktadır.

Contents |

Nano Dizinler ile Hesaplama | |||||||||||||||||||||||||||||||||||||||||||||

|

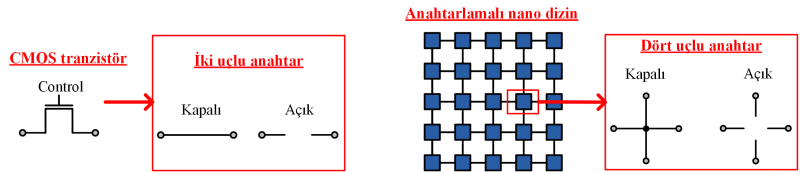

CMOS tranzistör boyutlarındaki küçülme trendi günümüzde kritik bir noktaya ulaşmıştır ve bu trendin yakın gelecekte sonlanacağı öngörülmektedir. Bu noktada araştırmalar yeni nanoteknolojilere ve moleküler düzeyde kendiliğinden üretilebilen (self-assembled) sistemlere kaymaktadır. Litografi gibi karmaşık yollarla üretilen geleneksel CMOS tabanlı teknolojilerden farklı olarak, nano düzeydeki teknolojiler genellikle düzenli yapılardan oluşmaktadır. Bu teknolojilerde lojik fonksiyonlar nano dizinlerdeki çaprazlayıcı anahtarlarla gerçeklenmektedir. Önerdiğimiz model, dört uçlu anahtarlardan oluşan ağlar, bu tip nano dizinlere yöneliktir. Modelimiz nanotel anahtarlamalı dizinler ve manyetik nano anahtarlamalı devreler gibi birçok yeni nano düzeydeki teknolojiye uygulanabilmektedir. SentezClaude Shannon 1947 yılında sunduğu mastır tezinde devrim niteliğinde bir hesaplama modeli sunmuştur. Bu model ile Shannon, herhangi bir Boolean fonksiyonun iki uçlu anahtarlardan oluşan bir ağ ile gerçeklenebileceğini göstermiştir. Shannon’ın bu çalışması milyarlarca tranzistörlerden oluşan modern CMOS devrelerin temelini oluşturmaktadır. Biz bu çalışmada dört uçlu anahtar bazlı yeni bir model sunduk ve bu model ile herhangi bir Boolean fonksiyonun gerçeklenebileceğini gösterdik. Modelimizin nano dizin tabanlı devre tasarım tekniklerine temel oluşturması amaçlanmaktadır.  GüvenilirlikYüksek hata oranları içeren nano dizinler için matematiksel pörkülasyon teorisine dayanan yeni bir hata tolerans tekniği geliştirdik. Bu teknik ile dizinlerdeki rastgele hatalar tolere edilebilecek ve böylece Boolean fonksiyonları güvenilir olarak gerçeklenebilecektir.

| |||||||||||||||||||||||||||||||||||||||||||||

Elektronik Kartların Güvenilirliği | |||||||||||||||||||||||||||||||||||||||

|

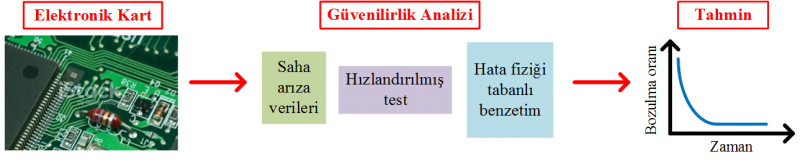

Elektronik sektöründe yaşanan baş döndürücü gelişmeler, elektronik devre ve sistemlerin güvenilirliği kavramını yeniden şekillendirmiştir. Elektronik ürünlerin günümüzdeki hızlı üretim döngüleri, uzun süreli ve masraflı olan geleneksel hızlandırılmış testlerin öneminin azalmasına neden olmuştur. Biz bu çalışmada görece masrafsız ve yüksek doğruluklu bir güvenilirlik analizi metodolojisi önerdik. Bu noktada saha verileri, yeni hızlandırılmış testler ve hata fiziği tabanlı benzetimlerden yararlandık. Çalışmalarımız Avrupa'nın en büyük ev aletleri ve beyaz eşya üreticilerinden biri olan Arçelik A.Ş. ile birlikte yürütülmektedir.  Saha Verileri ile Analiz ve TahminElektronik kartların saha arıza verilerini kullanarak güvenilirlik analizi yaptık. Analizimiz filtreleme ve modelleme aşamalarından oluşmaktadır. Filtreleme aşamasında, açık ve gizli hataların yer aldığı uygunsuz verileri tüm veri setinden eledik. Modelleme aşamasında, filtrelenmiş verileri kullanarak parçalı güvenilirlik modelimizi geliştirdik. Güvenilirlik analizimiz, verilerin ileri ve geri yönde incelenmesine dayanan yeni bir yaklaşımdır. Elektronik kartların kısa süreli saha verilerini kullanarak, garanti süresi içerisindeki güvenilirlik performanslarını yüksek doğrulukta tahmin ettik. Bu çalışmada kullandığımız kartların garanti süresi 3 yıldır ve kullandığımız veri seti 3 aylıktır.

| |||||||||||||||||||||||||||||||||||||||

Kuantum Devre Tasarımı | ||||||||||||||||||||||||||||||

Sentez ve OptimizasyonTersinir Boolean fonksiyonları kuantum kapılar ile gerçekleyen hızlı bir algoritma önerdik. Önerdiğimiz algoritma, her bir fonksiyon için zaman alıcı bir arama yapmak yerine temel fonksiyonları kullanmaktadır ve sonrasında sıralama yapmaktadır. Örnek vermek gerekirse, toplamda 20922789888000 fonksiyonun olduğu 4 bit devrelerdeki temel fonksiyon sayısı yalnızca 120'dir. Kuantum kapıların fiziksel yapılarını incelediğimizde, literatürde optimum alan olarak sunulan çözümlerin aslında optimum olmadığını gösterdik ve bu çözümleri iyileştirdik.

| ||||||||||||||||||||||||||||||

Analog Devre Tasarımı | |||||||||||||||

Pozitif GeribeslemeGeleneksel olarak analog devreler pozitif geribesleme çevrimleri içermemelidirler. Aykırı gözükse de, biz bu çalışmada akım kuvvetlendiricilerin giriş empedanslarını pozitif geribesleme kullanarak başarıyla iyileştirdik. Ek olarak yeni bir tamamen farksal akım kuvvetlendirici devresi önerdik ve bu devreyi filtre uygulamalarında test ettik.

| |||||||||||||||

Ayrık Matematik | |||||||||||||

"Self Duality" ProblemiIDNF (irredundant disjuntive normal form) formundaki monoton bir Boolean fonksiyonun self-dual olup olmadığının zaman karmaşıklığında belirlenmesi, matematikte çözülememiş önemli problemlerden biridir. Bu çalışma bu ünlü problem üzerinedir. Biz bu çalışmada IDNF formundaki monoton Boolean fonksiyonların değişken sayısının çarpım (disjunct) sayısından fazla olamayacağını gösterdik. Ayrıca n sayıda çarpım ve n sayıda değişken içeren IDNF formundaki monoton Boolean fonksiyonların, self-dual olup olmadığını bulan bir algoritma geliştirdik. Algoritmanın zaman karmaşıklığı O(n^3)'dür.

| |||||||||||||