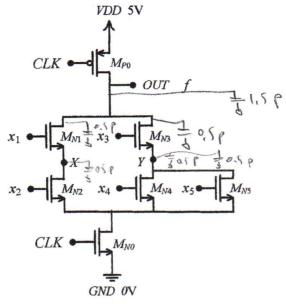

Suppose that each transistor has an internal grounded gate capacitor C<sub>G</sub> and drain capacitor C<sub>D</sub>:

$C_G = c_{ox}W L$ ;  $C_D = (c_{ox}W L)/2$ ;  $c_{ox} = 1 pF/um^2$ .

- Suppose that all NMOS transistors are identical and all PMOS transistors are identical.

- $W_{N0}=W_{N1}=W_{N2}=W_{N3}=W_{N4}=W_{N5}=1u$ ,  $W_{P0}=3u$ , and  $V_{TN}=|V_{TP}|=1V$ .

Dynamic Logic Circuit

- a) Derive a Boolean expression of f in terms of the inputs  $x_1$  through  $x_5$  in evaluation phase.

- b) At the start of the evaluation phase suppose that  $x_1 = 0 \rightarrow 1$ ,  $x_2 = 0$ ,  $x_3 = 0 \rightarrow 1$ ,  $x_4 = 0$ ,  $x_5 = 0$ , and  $V_X = 0$ V,  $V_Y = 0$ V,  $V_{OUT} = 5$ V. Considering the charge share problem, find the final voltage value at the output.

- c) To make the final voltage value at the output as 4.5V, determine the capacitor value of a load to drive.